Xilinx ( Xilinx Foundation Series) adalah suatu perangkat lunak yang berguna untuk merancang dan mensimulasikan suatu rangkaian digital. Dengan menggunakan Xilinx

proses perancangan suatu alat atau rangkaian digital melalui proses

simulasi rangkaian yang telah dirancang untuk melihat apakah rancangan

yang telah dibuat sudah benar atau masih mengandung kesalahan.

Sebenarnya tahapan atau proses perancangan alat atau rangkaian digital menggunakan Xilinx sama seperti merancang suatu rangkaian logika secara manual akan tetapi kelebihan menggunakan simulator Xilinx dapat diminimalisasi kesalahan pada proses perancangan. Sebelum mulai merancang rangkaian pada Xilinx minimal sudah dilakukan rancangan state diagram atau tabel kebenaran (truth tables)

dari spesifikasi rangkaian atau alat yang ingin dibuat. Kalau tidak

mempunyai rancangan tersebut, Xilinx tidak dapat membantu dalam

merancang alat tersebut.

Untuk perancangan rangkaian digital

, Xilinx mempunyai tiga cara yaitu dengan menggunakan State Diagram, HDL

(Hardware Description Language) dan Schematic.

- Metode Schematic

Suatu

rancangan rangkaian dapat diwujudkan ke dalam FPGA dengan cara menggambar skema

rangkaian tersebut. Penggambaran skema rangkaian tersebut dapat dilakukan pada

perangkat lunak (software). FPGA buatan Xilinx dengan perangkat lunaknya yakni

ISE WebPack. Skema rangkaian di gambar dengan cara membuat tiap komponen serta

jalur-jalur yang menghubungkan komponen-komponen tersebut menjadi satu

kesatuan. Metode ini terbilang mudah dan efektif terutama bila dipakai untuk

skema rangkaian yang sederhana serta tidak memiliki jalur-jalur yang rumit.

Skema

desain skematik merupakan seperangkat system yang memungkinkan untuk menangkap

struktur desain baik sebagai deskripsi datar atau hirarkis seperangkat komponen

, dan konektivitas antara komponen-komponen tersebut. Schematic dapat

single-level (flat) atau multi-tingkat(hirarkis).

- Metode HDL(Hardware Description Language).

Metode

lain yang digunakan merancang rangkaian ialah menggunakan Bahasa Deskripsi

perangkat Keras. Kode untuk HDL ada dua yaitu Verilogn dan VHDL. Verilog dan

VHDL lebih terkenal karena mudah dipahami dan dimengerti. Metode ini lebih

banyak digunakan daripada metode schematic.

Cara Penggunaan Xilinx

- Buka Program Xilinx

| |

| Tampilan awal dari Xilinx |

- Buat Project baru dengan cara buka tab File dan pilih New Project... maka akan terdapat tampilan seperti di gambar di bawah. Setelah itu beri nama project dan klik tombol Next sebanyak 4 kali untuk melanjutkan proses dan di akhiri tombol Finish

- Klik kanan, pilih new source seperti gambar dibawah ini:

- Pilih

schematic, dan ketik file name (untuk file name bebas). Seperti

gambar dibawah:

- Klik nextàklik finish

- Maka akan muncul layar seperti gambar berikut ini:

Langkah-Langkah

Mendasain Rangkaian:

- Setelah mengikuti langkah diatas, maka langkah selanjutnya untuk mendesain sebuah rangkaian.

- Pilih source, posisinya di pojok kiri atas seperti gambar diatas.

- Pilih Symbol Name Filter, masukan nama gerbang yang akan dirancang, misalnya gerbang OR. Seperti gambar dibawah ini:

Langkah –Langkah Simulasi

Rangkaian:

- Klik source , seperti gambar dibawah ini:

- Klik Synthesis-XST > View Synthesis Report. Proses selesai, selanjutnya,

- Klik Implement Design> Translate> Map> Place and Route.

- selanjutnya, pilih source> source for> Behavioral Simulation, seperti gambar dibawah ini.

- Klik kanan pada nama file yang anda buat, pilih new source

- Pilih Test Bench WaveForm, ketik file name (bebas) seperti dibawah ini:

- Klik Next > Next > Finish

- Selanjutnya, pilih Combinational > High For Initial di kosongkan , seperti gambar dibawah ini:

- Klik Finish, selanjutnya masukan inputan logika yang telah ditentukan. Seperti gambar berikut ini:

- Klik file, pilih save.

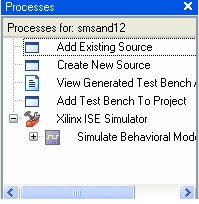

- Selanjutnya pilih Processes Dibagian pojok kiri bawah, seperti gambar berikut ini:

- Double klik Simulate Behavioral Model.

- Proses selesai dan output dapat dilihat.

Sintesis adalah

adalah alat pemetaan RTL untuk setiap

program , juga melakukan minimal waktu

analisis untuk melihat apakah desain yang di petakan memenuhi persyaratan atau

tidak.

Simulasi adalah

proses verifikasi karakteristik fungsional model pada setiap tingkat abstraksi.

Referensi:

http://www.adityarizki.net/2011/06/tutorial-teknik-digital-dengan-xilinx-mengenal-xilinx/

http://www.2shared.com/complete/ecSMeqWa/TUTORIAL__XILINX_ISE_92i_Prak_.html

Tidak ada komentar:

Posting Komentar